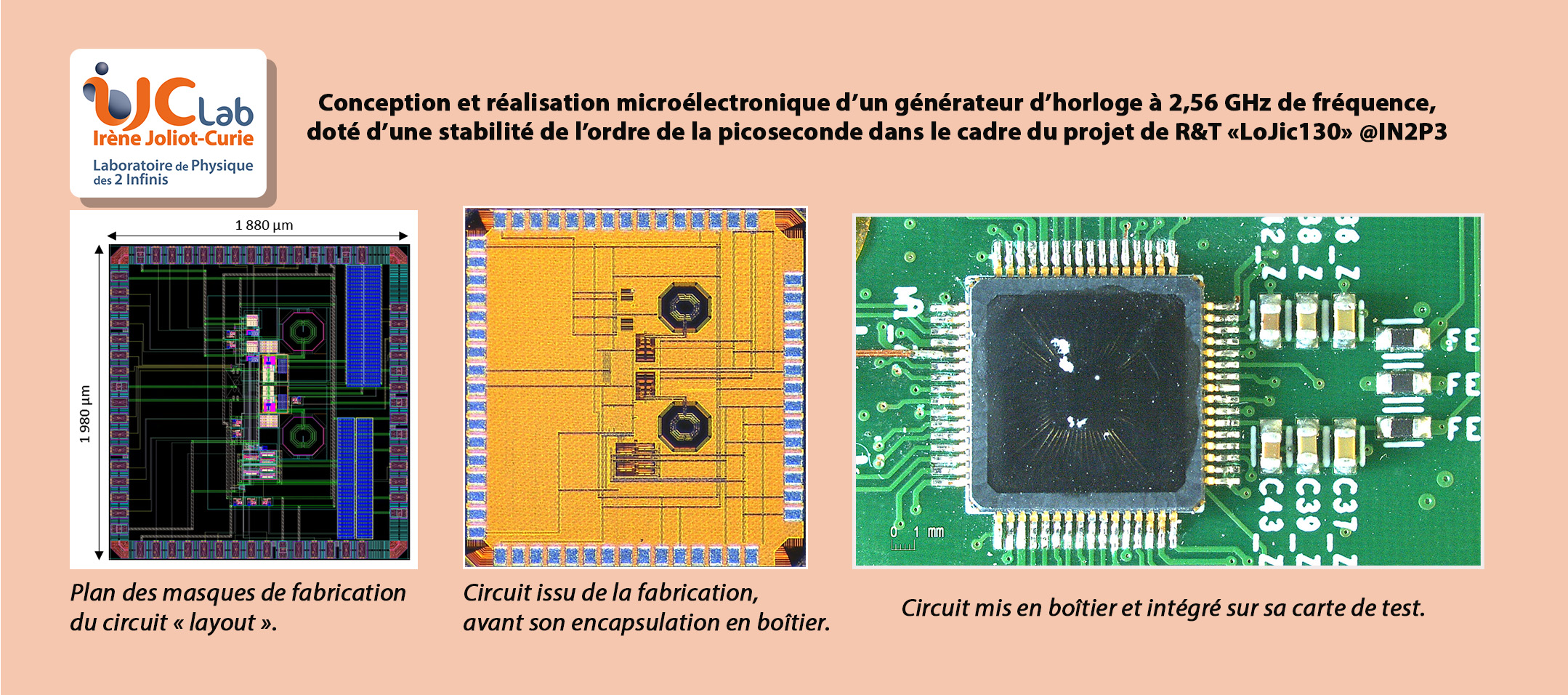

Dans le cadre de son expertise en mesures de temps à haute résolution, le Service Développements Analogiques et Microélectronique (Pôle Ingénierie, Département Électronique) a contribué au projet de R&T IN2P3 « Lojic130 » porté par le pôle MicRhAu. Il a pour objectif de réaliser un générateur d’horloge à haute fréquence possédant une stabilité de l’ordre de la picoseconde. Ce type de générateur d’horloge microintégré est un élément essentiel des instruments de mesure de temps (TDC : Time to Digital Converter) requis pour assurer le marquage en temps de l’instant d’arrivée des signaux issus des détecteurs de particules.

En effet, dans le futur LHC Haute Luminosité (HL-LHC) le nombre de collisions proton-proton simultanées doit passer de 40 actuellement au LHC, à près de 200. L’empilement des signaux va devenir tel que de nouvelles stratégies d’enregistrement doivent être développées afin d’aider à démêler un à un chaque jaillissement de particule dans les détecteurs. Un axe majeur de développement poursuivi par plusieurs expériences de physique (Atlas@HGTD, CMS@HGCAL, ECAL2@LHCb, TOF-PET...) consiste à effectuer un découpage temporel de chaque prise de vue des détecteurs grâce à un traitement électronique ultra fin. En d’autres termes, il s’agit d’étiqueter précisément l’instant d’arrivée de milliers de signaux dans une même prise de vue. De cette manière, les physiciens et physiciennes pourront reconstituer le film de la formation de l’image finale et relier plus facilement les différentes traces les unes aux autres.

Dans ce contexte, un circuit spécifique (ASIC : Application Specific Integrated Circuit) à base de « boucles à verrouillage de phase » (PLL : Phase Locked Loop) à très faible gigue temporelle (jitter) a été conçu en technologie TSMC 130 nm. Au retour de la fonderie de ce circuit, la caractérisation du prototype a permis de qualifier un « jitter » d’environ 2 ps RMS sur l’horloge à 2,56 GHz de fréquence, délivrée par ce circuit. Les microélectroniciens d’IJCLab ont assuré en particulier la conception de la partie garantissant à cette « PLL » un asservissement stable et précis, c’est-à-dire le détecteur de phase et de fréquence et sa pompe de charge associée qui sont constitués de structures CMOS « full custom » à la fois analogiques et numériques. Compte tenu des performances obtenues, cette PLL sera transposée en technologie TSMC 65 nm pour être intégrée dans l’ASIC « SPIDER » (Swift Pipelined Digitizer) dont le but est de répondre aux besoins spécifiques en mesure de temps consécutifs à la jouvence phase 2 du Calorimètre Électromagnétique de l’expérience LHCb au CERN. La version prototype de l’ASIC « SPIDER » qui est en cours de conception à IJCLab, en collaboration avec les laboratoires LPC, IP2I et LPCC, sera finalisée pour la fin d’année 2023.

L'article paru sur le site Actualités de l'IN2P3.