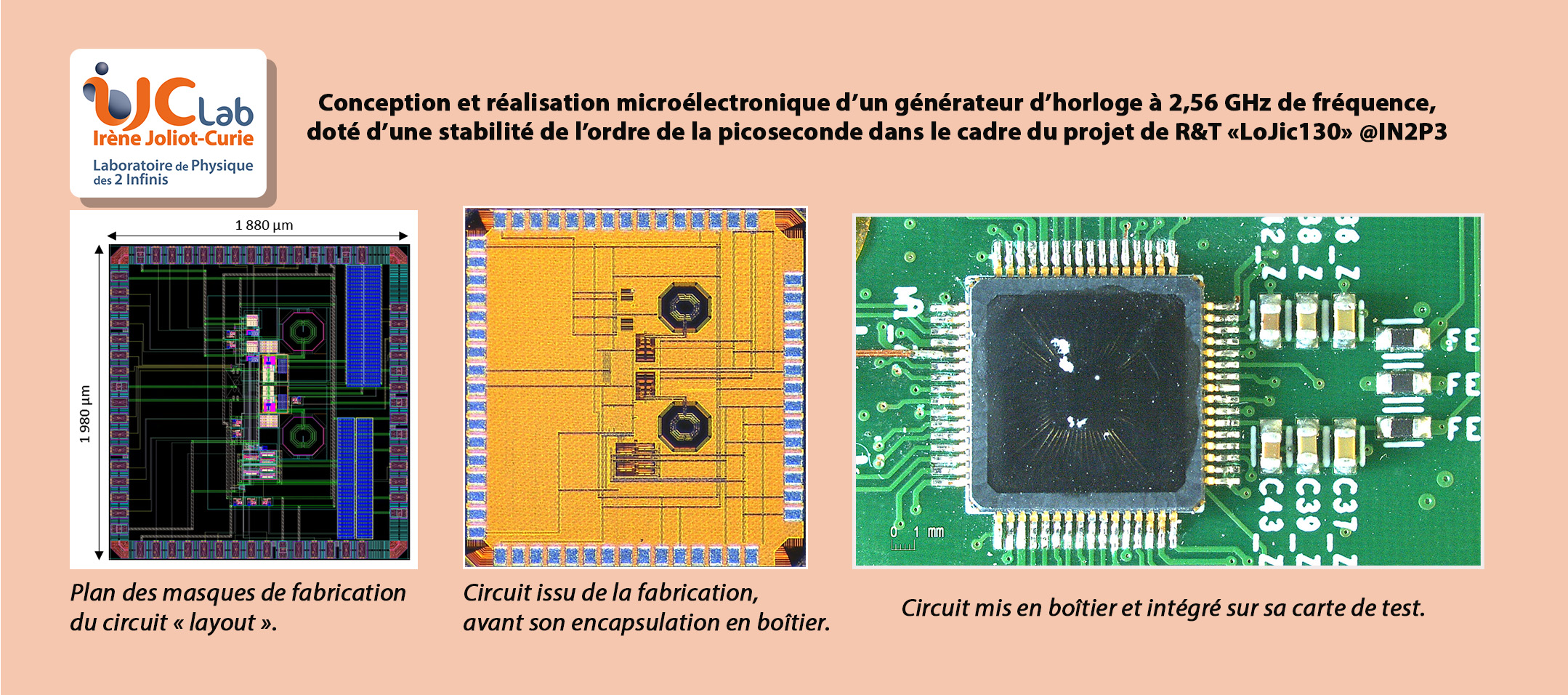

As part of its expertise in high-resolution time measurements, the Analog and Microelectronics Development Department (Engineering Pole, Electronics Department) contributed to the IN2P3 "Lojic130" R&T project led by the MicRhAu pole. Its objective is to produce a high-frequency clock generator with a stability of the order of a picosecond. This type of microintegrated clock generator is an essential element of the time measurement instruments (TDC: Time to Digital Converter) required to ensure the marking in time of the instant of arrival of the signals from the particle detectors.

Indeed, in the future High Luminosity LHC (HL-LHC) the number of simultaneous proton-proton collisions must increase from 40 currently at the LHC, to nearly 200. The stacking of signals will become such that new recording strategies must be developed in order to help disentangle one by one each burst of particle in the detectors. A major line of development pursued by several physics experiments (Atlas@HGTD, CMS@HGCAL, ECAL2@LHCb, TOF-PET, etc.) consists in performing a time division of each detector shot using ultra-high electronic processing. In other words, it is a question of precisely labeling the instant of arrival of thousands of signals in the same shot. In this way, physicists will be able to reconstruct the film of the formation of the final image and more easily connect the different traces to each other.

In this context, a specific circuit (ASIC: Application Specific Integrated Circuit) based on “phase locked loops” (PLL: Phase Locked Loop) with very low temporal jitter (jitter) was designed in TSMC 130 nm technology. Upon return from the foundry of this circuit, the characterization of the prototype made it possible to qualify a "jitter" of approximately 2 ps RMS on the clock at 2.56 GHz frequency, delivered by this circuit. IJCLab's microelectronics engineers in particular ensured the design of the part guaranteeing this "PLL" a stable and precise servo-control, i.e. the phase and frequency detector and its associated charge pump which are made up of "full custom" CMOS structures, both analog and digital. Given the performance obtained, this PLL will be transposed into TSMC 65 nm technology to be integrated into the "SPIDER" ASIC (Swift Pipelined Digitizer) whose purpose is to meet the specific needs in time measurement following the phase 2 rejuvenation of the Electromagnetic Calorimeter of the LHCb experiment at CERN. The prototype version of the "SPIDER" ASIC which is being designed at IJCLab, in collaboration with the LPC, IP2I and LPCC laboratories, will be finalized by the end of 2023.

The article published on the IN2P3 News site.